# embedded VISIMN Summit

Cadence Tensilica Edge Al Processor IP Solutions for Broad Market Use Cases

Pulin Desai Group Director, Vision & Al Product Marketing September 2020

cādence<sup>®</sup>

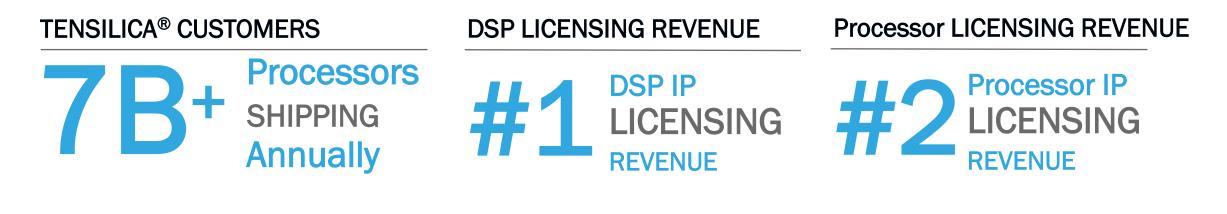

## **Cadence Tensilica Processor and DSP IP Business**

## **Examples of Edge AI: Voice & Vision**

cādence

Mobile

#### **Smart Surveillance**

Vision AI

**AR/VR**

**Autonomous Vehicles**

## **Processing Flow for Inference in the Embedded System**

Sensing Pre Post Inference The outside Processing Processing World Where does data come from? Preparing the  $\triangleright$ Any post processing  $\geq$ Al to analyze the incoming data  $\geq$ Image sensor data for Analysis of data Radar Vision  $\geq$ AI has other layers which are beyond Lidar convolution Microphone Voice

embedded

- Any sensing application always has a pre & post processing

- Need to solve the whole data path

## cādence<sup>°</sup>

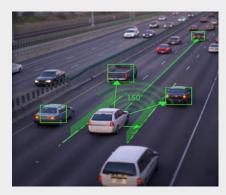

## Machine Learning Innovations Using Microphone as a Sensor

embedded

<u>Privacy, latency, power</u>, and <u>availability of network drives</u> <u>voice UI and other ML applications</u> to edge devices

#### cādence°

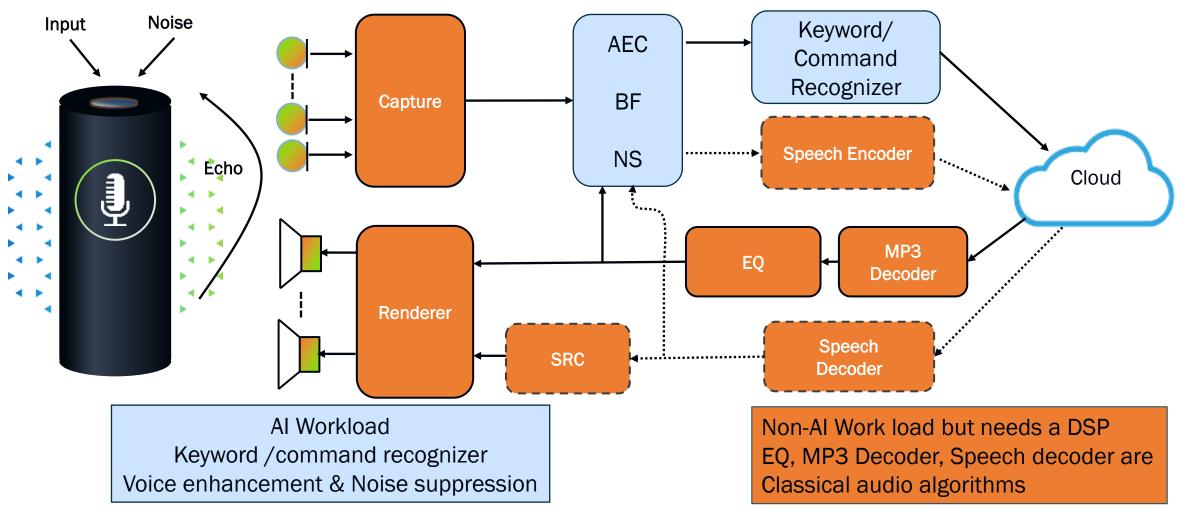

### **System Integration – Smart Speaker Example**

#### cādence°

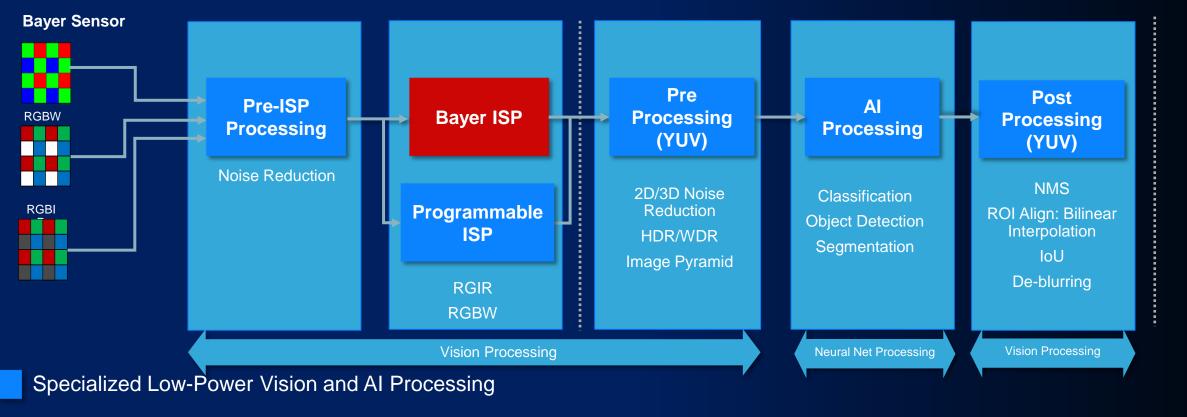

## **Computer Vision and Image Processing Pipeline**

Usually a Hardware Block

cādence

• Any Vision application has a pre & post processing

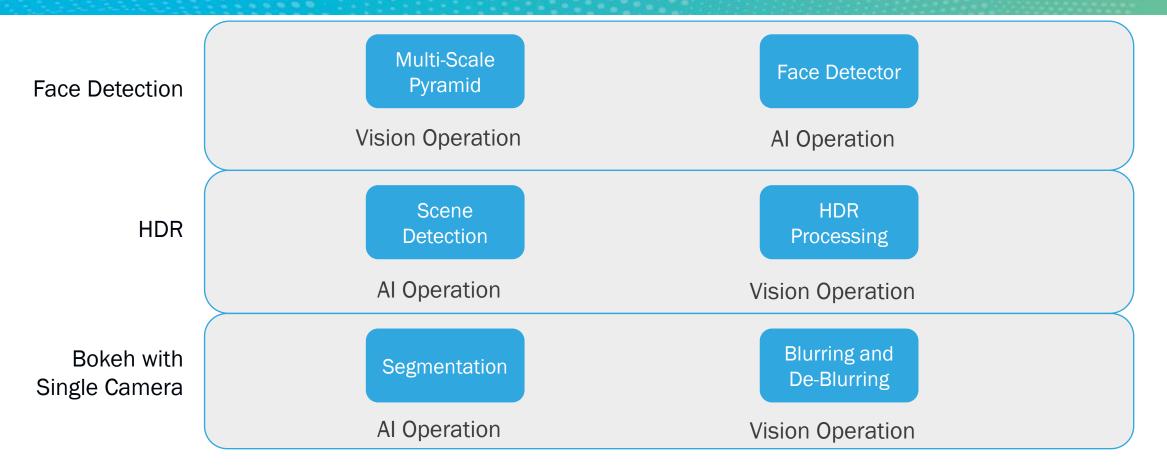

## **Vision Applications: Mix of Vision and AI**

- All use cases still have mix of vision and AI operations

- Need for both vision and AI processing in the camera pipeline

cādence<sup>°</sup>

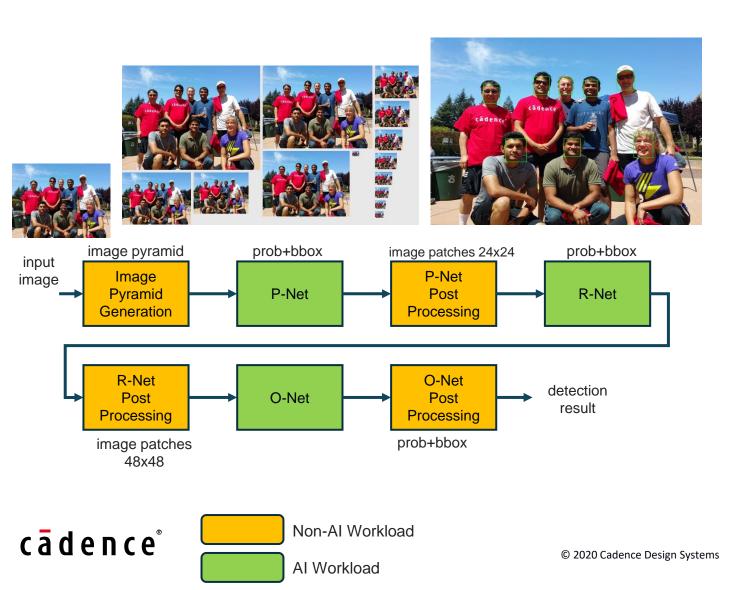

## Multi Net Application Case Study MTCNN: A Face Detection Neural Network

In MTCNN use case with 3 separate nets (P/O/R), <u>glue processing is</u> <u>inserted between the nets to perform</u> <u>end to end face detection</u>

Even if entire networks are sped up the application <u>speedup will be</u> <u>bottlenecked by glue processing which</u> does not need to be "standardized"

<u>A high performance DSP</u> targeted at Vision applications can keep up with the evolving glue processing requirements

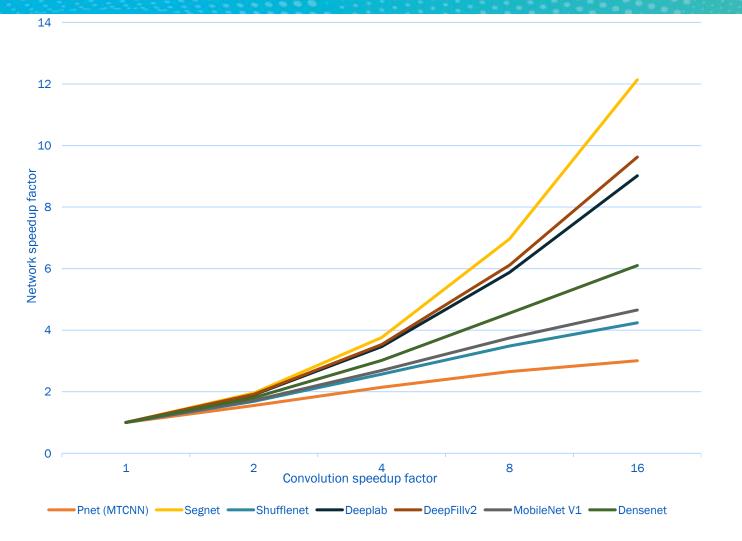

## Hypothetical Speedup when only Convolution is Accelerated

- Convolutions are common target for acceleration with hardware

- As convolutions speed up, different networks will achieve varying amounts of overall speedup

- <u>Some networks achieve only</u> <u>modest speedups</u> <u>bottlenecked by "other"</u> <u>layers</u>

- "Other" layers need to keep up with convolutions acceleration

#### cādence°

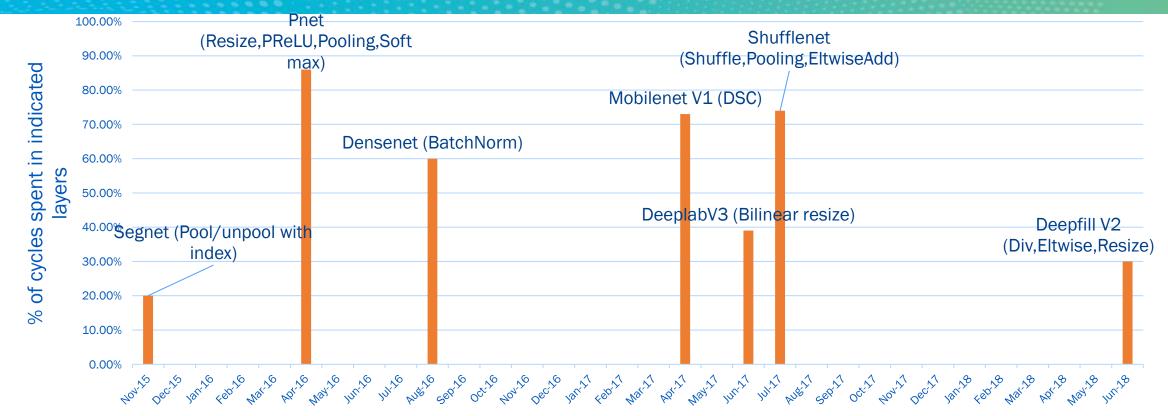

## **Significant Cycle Consuming Non-Convolution Layers**

- The set of "other" layers is large and continuously evolving

- Non-convolution layers can be 20% to as high as >80% of the cycles

- A high performance DSP targeted at NN applications can keep up with the evolving requirements

#### cādence<sup>°</sup>

## **Neural Network Deployment Options in Embedded Systems**

| Metric:<br>Option                   | Flexibility                  | Power     | Performance               | Time to Market                                |

|-------------------------------------|------------------------------|-----------|---------------------------|-----------------------------------------------|

| CPU                                 | ✓ Highly flexible            | Very high | Depends                   | Fast                                          |

| CPU+GPU                             | ✓ Highly flexible            | Very high | Depends but could be high | Fast                                          |

| Hardware<br>Development             | Not flexible                 | Low       | High                      | Long development<br>cycle and<br>verification |

| Programmable DSP                    | $\checkmark$ Highly flexible | ✓ Low     | Depends                   | ✓ Fast                                        |

| Programmable DSP+<br>HW accelerator | $\checkmark$ Highly flexible | ✓ Low     | High                      | ✓ Fast                                        |

#### cādence<sup>°</sup>

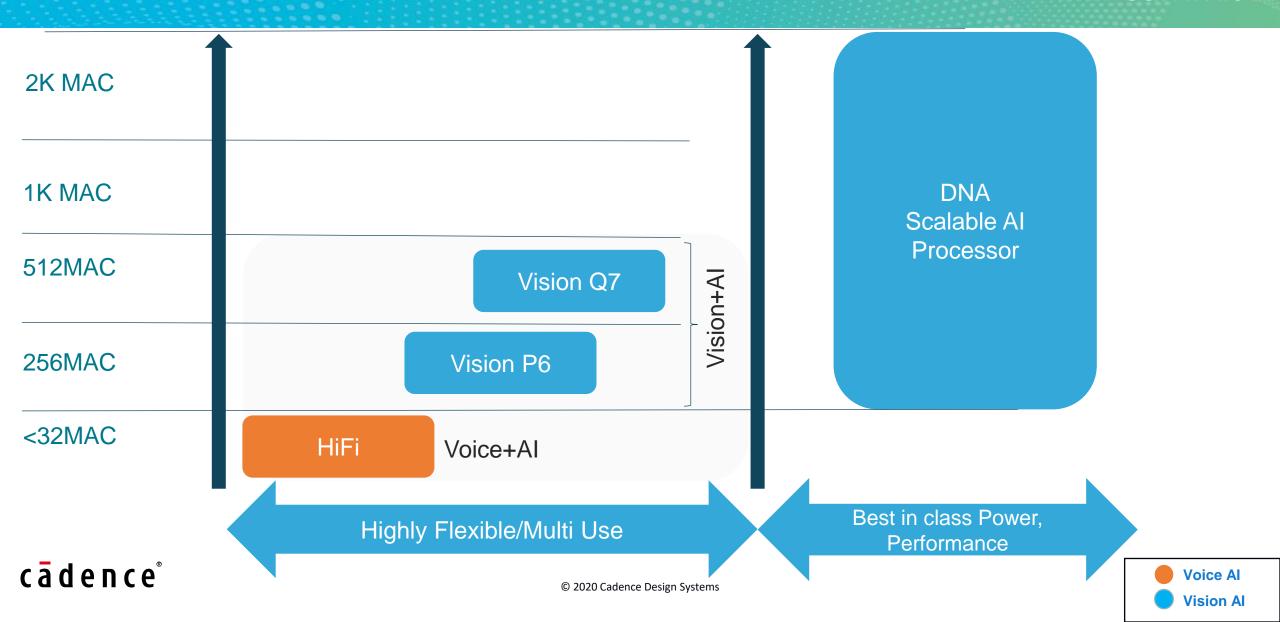

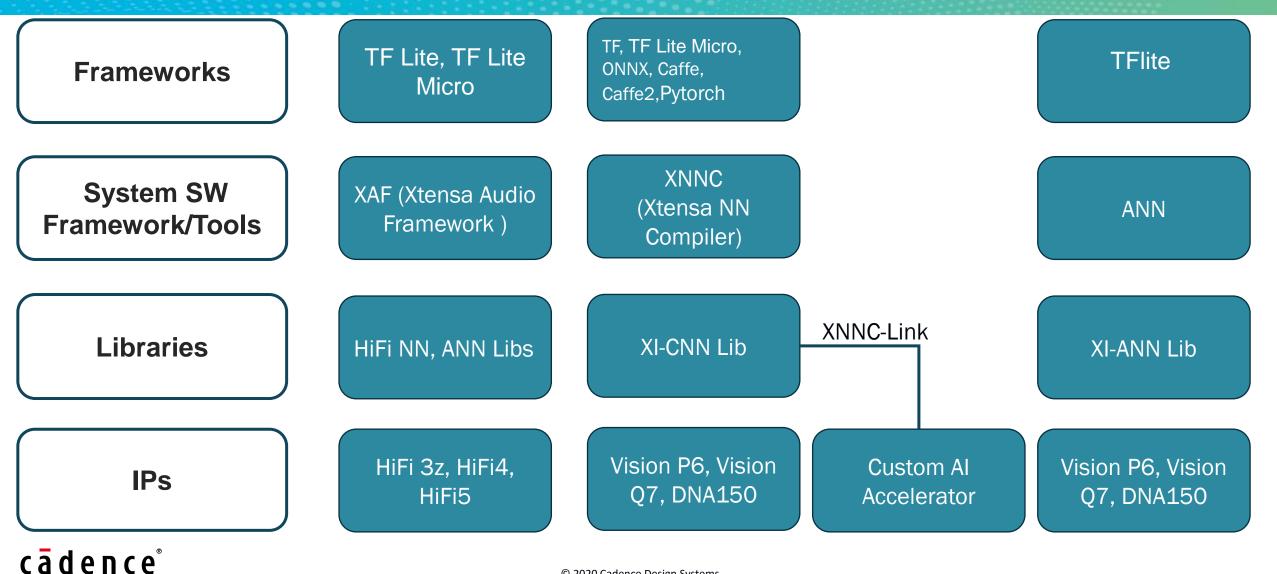

## **Tensilica AI Portfolio: AI Inference at the Edge**

embedded

## **HiFi DSP Is Ideal for ML Solutions on the Edge**

Tensilica<sup>®</sup> HiFi DSP is the leading IP solution for audio, speech, and machine learning applications

Cadence enables developers to train and seamlessly deploy their machine learning applications on HiFi DSPs using TensorFlow Lite for Microcontrollers

HiFi DSP has extensive production-ready software solutions from Cadence and the largest ecosystem with 160+ software partners

Tensilica<sup>®</sup> Xtensa Audio Framework (XAF) accelerates integration of ML and traditional audio workloads, reducing time to market

#### cādence<sup>®</sup>

## Vision P6/Q7: Ideal DSP for Vision + AI

| Vision Acceleration  | <ul> <li>512-bit SIMD</li> <li>5 VLIW Slots</li> <li>8bit/16bit/32bit int, SP and HP FP Support</li> <li>0.7 to 1.7 TOPS</li> </ul>                                      |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI Acceleration      | • 256/512 8-bit MAC<br>• FP16 support                                                                                                                                    |

| High Data Throughput | <ul> <li>1024 bit memory I/F</li> <li>Scatter Gather Technology</li> <li>Multi-channel iDMA</li> <li>128/256 bit Axi</li> </ul>                                          |

| Lib & Tools          | <ul> <li>OpenCV Base imaging/vision Lib, SLAM Lib</li> <li>OpenCL, Halide, OpenVX Support</li> <li>NN Compiler (ONNX &amp; GLOW) &amp; Android NN API Support</li> </ul> |

| a d e n c e°         | © 2020 Cadence Design Systems                                                                                                                                            |

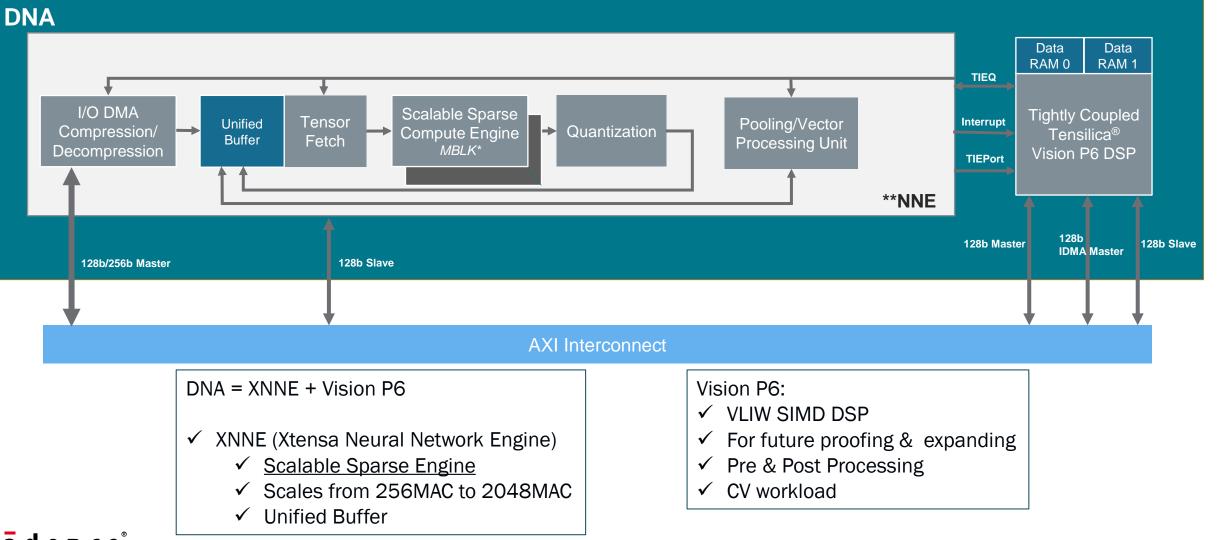

## Tensilica DNA Processor: Single Processor for Vision & Al Sparse Compute Engine & Scalable

#### cādence<sup>°</sup>

## **Typical Vision + AI Work: On Tensilica DNA Processor**

| Pre-Processing<br>Runs on Vision P6                   | Al Workload<br>(Convolution)<br>Runs XNNE HW of<br>DNA Processor   | Post-Processing<br>Runs on Vision P6                                                                                       |

|-------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Multi-scale Pyramid<br>Color-space<br>Noise Reduction | NN Workload<br>Mostly various convolution<br>Non-Convolution Layer | Non-Max Suppression (NMS)<br>ROI Align: Bilinear Interpolation<br>De-blurring<br>HDR                                       |

|                                                       | © 2020 Cadence Design Systems                                      | Example Networks:<br>Yolo, SSD, MaskRCNN, CRNN<br>Could be >10% cycles<br>Depends on # of detection<br>Depends on accuracy |

2020 embec

dec

cādence<sup>®</sup>

## **Tensilica AI SW Tools Portfolio**

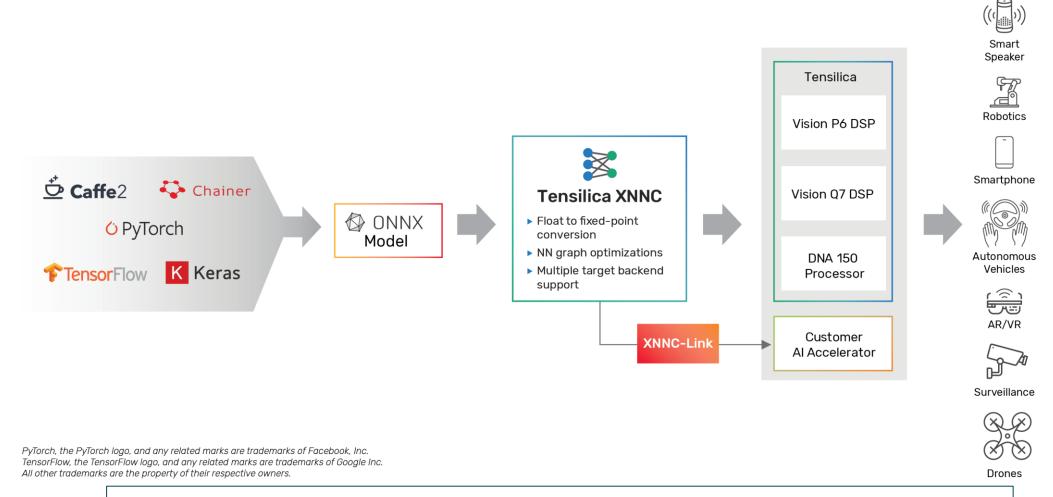

## XNNC-Link NN Code Generation for customer's AI Accelerator

cādence

Vision DSP + Customer's accelerator for your Al Solution

## **Edge-AI products with Cadence Tensilica AI IP**

| меділтек | "MediaTek has confirmed that the P60 integrates a <u>Cadence Vision P6</u><br><u>core</u> for its AI accelerator." Source (1)                                | NXP i.MX-RT600<br>HiFi 4 for audio and voice processing                                                                                                                                                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| меділтек | Mediatek i500 : " Al acceleration for APU based on <u>Tensilica Vision P6</u> (i500) " Source: (2)                                                           | "NXP's enablement for Glow is tightly coupled with the Neural<br>Network Library (NNLib) that Cadence provides for its <u>Tensilica</u><br><u>HiFi 4 DSP</u> delivering 4.8GMACs of performance."<br>Source: (5)                  |

| TOSHIBA  | "Toshiba Selects Cadence <u>Tensilica Vision P6</u> DSP as Image<br>Recognition Processor for its Next-Generation ADAS Chip" Source (3)                      | Baidu HongHu<br>HiFi 4 for audio and voice processing                                                                                                                                                                             |

| Gneron   | Kneron, the San Diego and Taipei-based low-power edge AI startup,<br>"KL720 NPU IP integrated with <u>Cadence Tensilica Vision P6 DSP IP</u> "<br>Source (4) | "Baidu today released its new chipset Honghu at the annual Al<br>Developer Conference in Beijing. It features <u>HiFi4</u> custom<br>instruction set, dual-core DSP, and only 100mV power<br>dissipation on average." Source: (6) |

- Source 3: https://www.mediatek.com/blog/mediateks-rich-iot-sdk-v20-0-release-available-now-for-i300-and-i500-chipset-series

- Source 4: https://www.eetimes.com/kneron-raises-40m-for-next-gen-edge-ai-chip/

- Source 5: https://media.nxp.com/news-releases/news-release-details/industrys-first-mcu-based-implementation-glow-neural-network

- Source 6: https://en.pingwest.com/w/2549

#### cādence<sup>°</sup>

Source 1: https://www.eetimes.com/mobile-ai-race-unfolds-at-mwc/#

Source 2: https://www.cadence.com/en\_US/home/company/newsroom/press-releases/pr/2019/toshiba-selects-cadence-tensilica-vision-p6-dsp-as-image-recogni.html

- ns embedde VISION SUMMI

- Voice+AI & Vision+AI for edge requires pre & post processing in addition to neural network processing

- In addition to convolution layers (which are MAC heavy) other layers take considerable cycles

- MAC acceleration only does not accelerate the AI performance

- Combination of hardware acceleration for convolution and programmable DSP provides the best solution for Edge AI workload

- Single hardware can be used for both concurrent Vision+AI and Voice+AI workload

- Cadence Tensilica provides Vision+AI and Voice+AI HW IP with NN Compiler SW

- Cadence Tensilica IP is shipping in large number of edge-ai products

## cādence°

## **Resource Slide**

**Cadence Resources**

https://www.cadence.com/en\_US/

home/tools/ip/tensilica-processorip.html

https://ip.cadence.com/vision https://ip.cadence.com/ai External Resources https://onnx.ai/ https://onnx.ai/supported-tools.html https://www.edge-aivision.com/2019/10/cadence-demonstrationof-a-recurrent-neural-network-based-showattend-and-tell-on-a-tensilica-dsp-platform/

# cādence®

© 2017 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. All other trademarks are the property of their respective owners.