**Deploying Deep Learning Application on FPGAs with MATLAB**

Jack Erickson

Technical Marketing

September 2020

## Deep Learning Deployment on Embedded Devices

#### Autonomous Driving

# Wireless Modulation Classification

#### **Industrial Inspection**

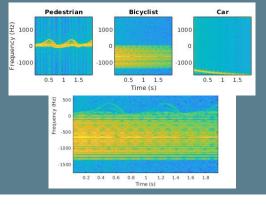

# Radar Signature Classification

# **System Requirements Drive Network Design**

Camera specs

Accuracy

Latency

Cost

Power

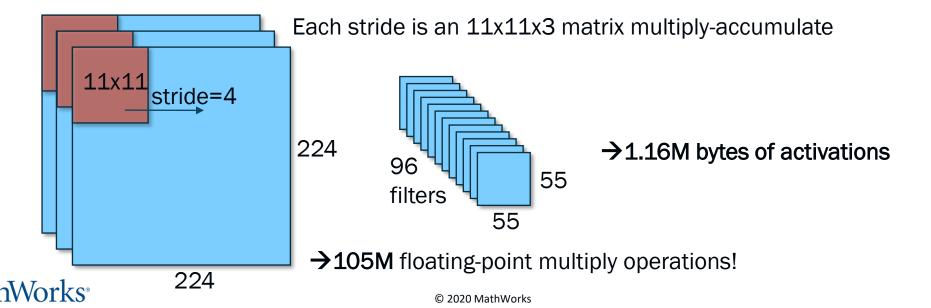

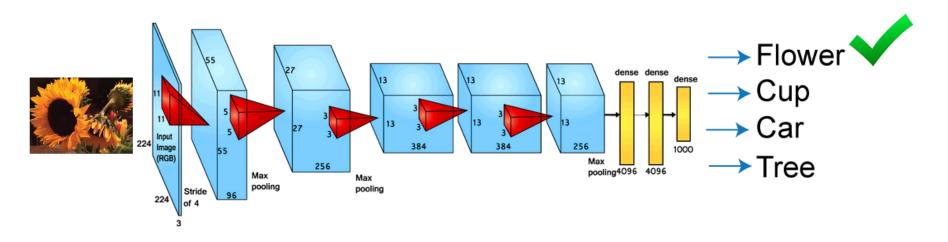

## **Challenges of Deploying Deep Learning to FPGA Hardware:** Convolution

Figure 1. Illustration of AlexNet.

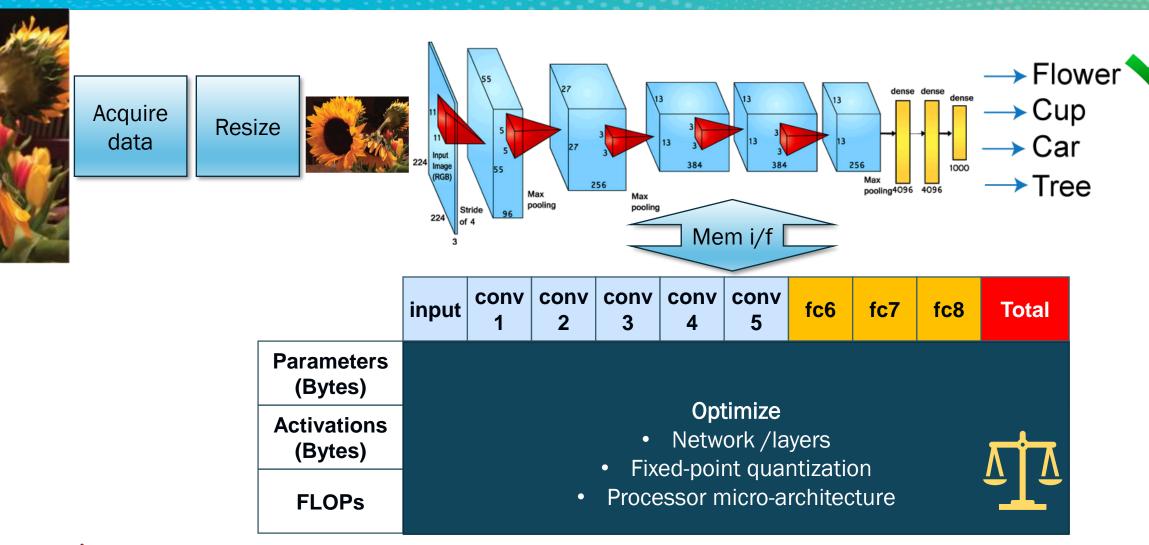

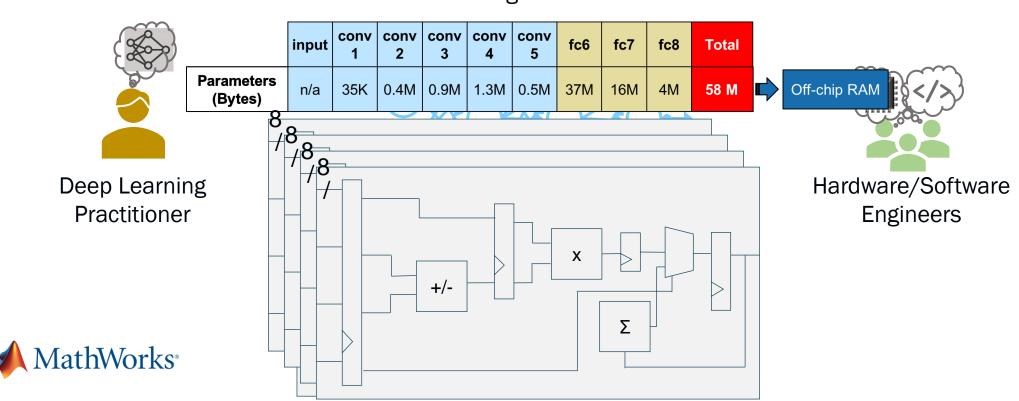

# **Challenges of Deploying Deep Learning to FPGA Hardware**

|                     | input | conv<br>1 | conv<br>2 | conv<br>3 | conv<br>4 | conv<br>5 | fc6  | fc7 | fc8 | Total |              |

|---------------------|-------|-----------|-----------|-----------|-----------|-----------|------|-----|-----|-------|--------------|

| Parameters (Bytes)  | n/a   | 140K      | 1.2M      | 3.5M      | 5.2M      | 1.8M      | 148M | 64M | 16M | 230 M | Off-chip RAM |

| Activations (Bytes) | 588K  | 1.1M      | 728K      | 252K      | 252K      | 168K      | 16K  | 16K | 4K  | 3.1 M | Block RAM    |

| FLOPs               | n/a   | 105M      | 223M      | 149M      | 112M      | 74M       | 37M  | 16M | 4M  | 720 M | DSP Slices   |

# **Deploying Deep Learning to FPGA Hardware Requires Collaboration**

Output /

display

#### A Collaborative AI Workflow

#### **Data Preparation**

Data cleansing and preparation

Human insight

Simulationgenerated data

#### **Al Modeling**

Model design and tuning

Hardware accelerated training

Interoperability

#### **System Design**

Integration with complex systems

- x System verification

- ─✓ and validation

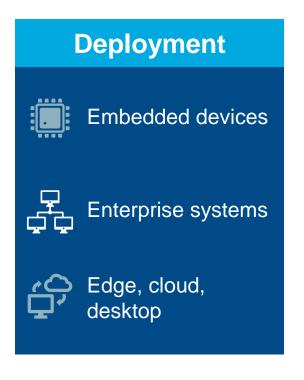

#### **Deployment**

Embedded devices

Enterprise systems

Edge, cloud, desktop

**Iteration and Refinement**

#### **Design and Analyze Your Networks in MATLAB**

#### **AI Modeling**

Hardware accelerated training

**Deep Network Designer** app to build, visualize, and edit deep learning networks

Classification Learner app to try different classifiers and find the best fit for your data set

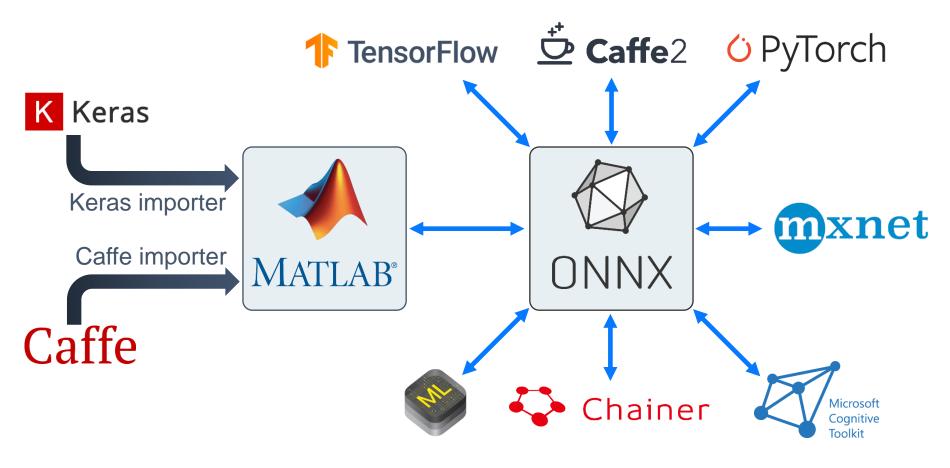

#### **MATLAB Interoperates with Other AI Frameworks**

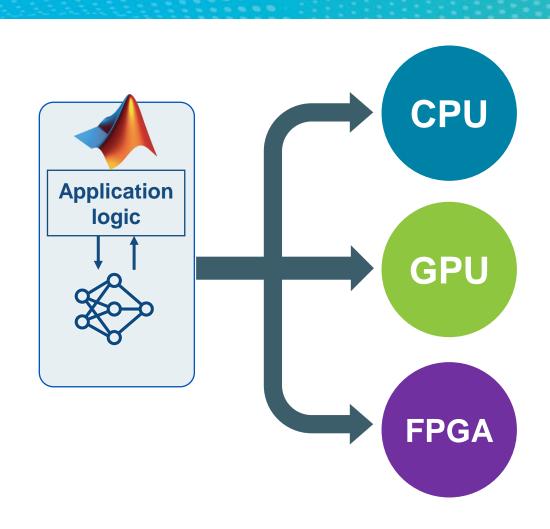

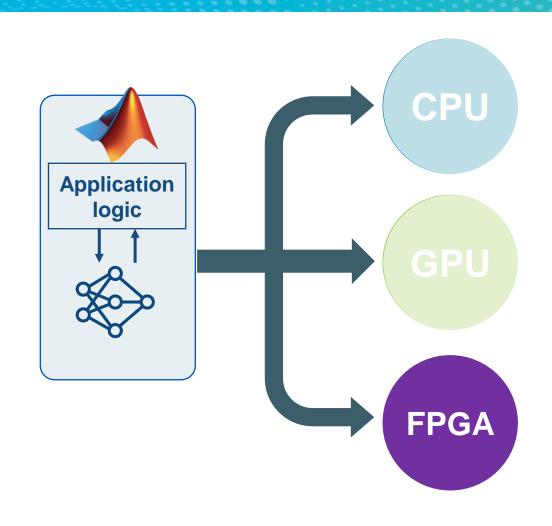

# **Deploy from MATLAB to a Variety of Hardware Platforms**

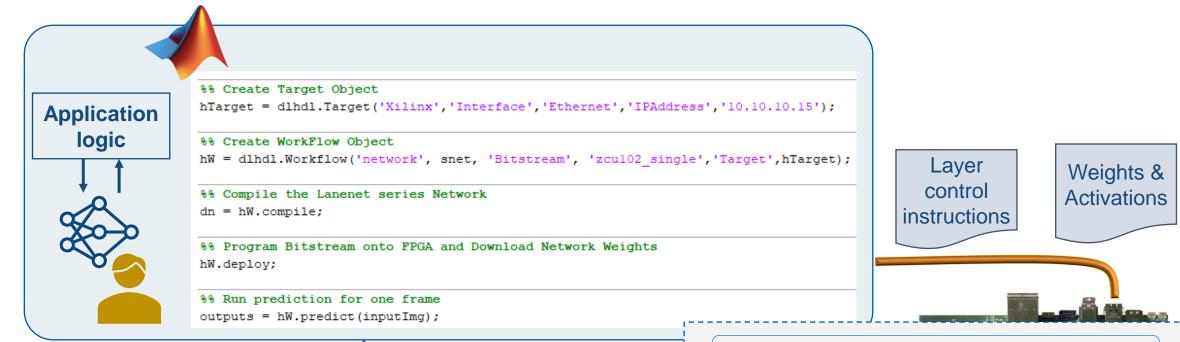

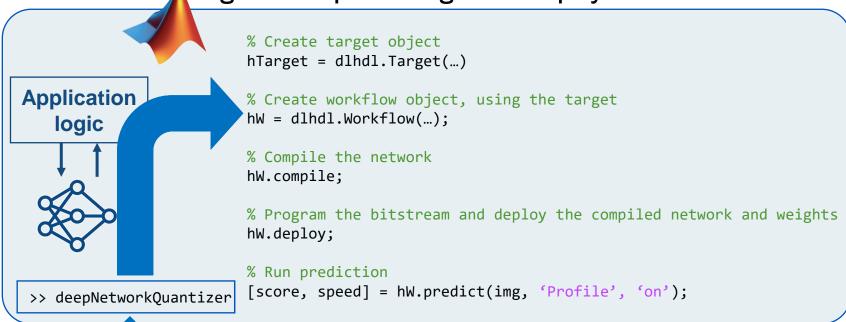

# **FPGA Deployment from MATLAB** MathWorks

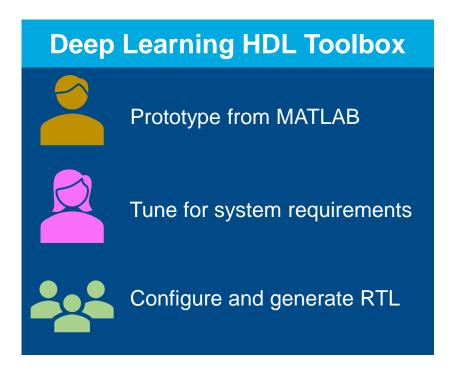

# Get Started Prototyping on FPGA with Deep Learning HDL Toolbox<sup>TM</sup>

Hardware support packate Deep learning processo external memory interfa

- Int8 or single precision

- Supported boards:

- Xilinx: ZCU102 or ZC

- Intel: Arria10 SoC

- http://mathworks.com/har

© 2020 MathWorks

#### Memory Access

Activation Convolution Module

Activations

Fully Connected Module Activations

**Processor Control**

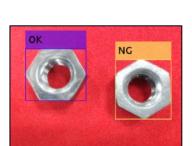

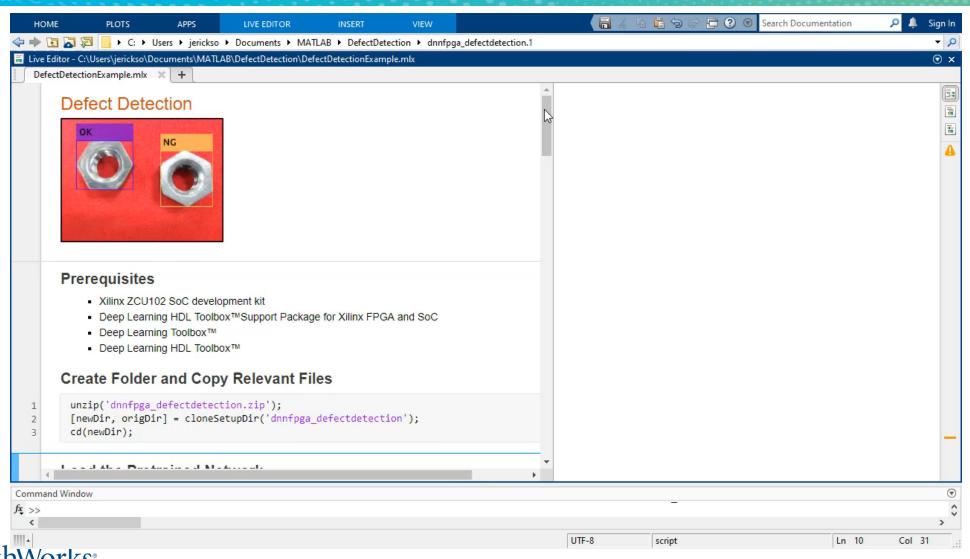

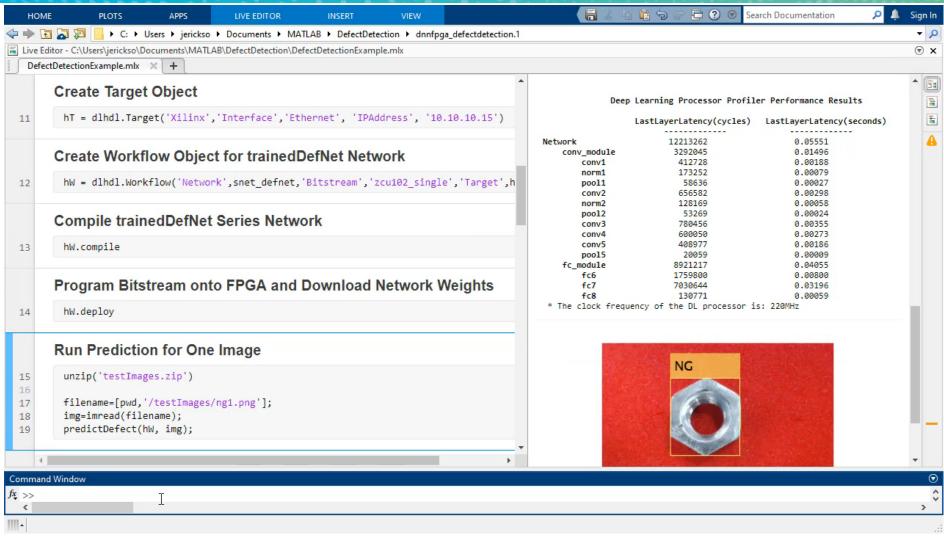

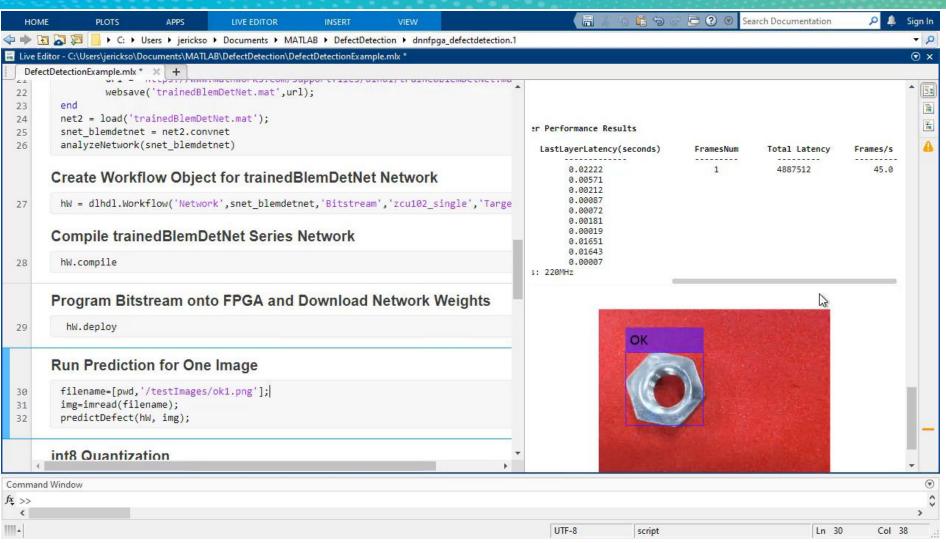

# **Defect Detection Example**

Pre-processing: Extract regions and resize

Inference: Predict using trained network

Post-processing: Annotate and label

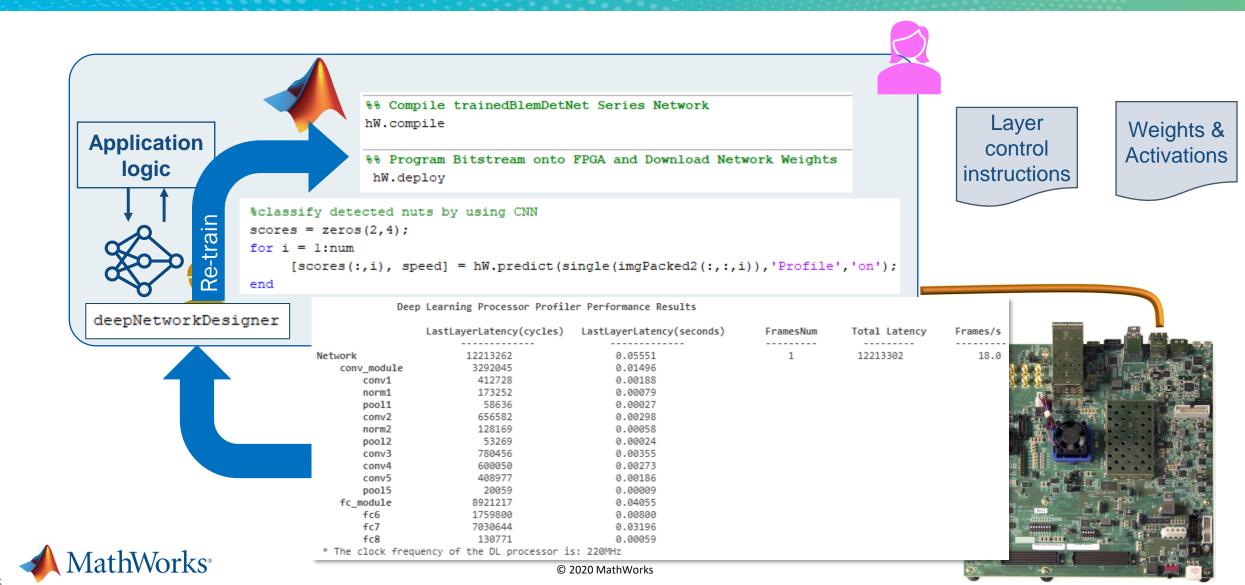

## Run Deep Learning on FPGA from MATLAB

# **Prototyping: Design Exploration and Customization**

## **Design Exploration and Customization**

16

# Optimizing Deep Learning Applications Requires Collaboration

Systems Engineer

#### **INT8 Quantization**

#### **Deep Learning HDL Toolbox**

#### Iterate and Converge on Deep Learning FPGA Deployment from MATLAB

Layer control instructions

Weights & Activations

Quantize

| Parameters | Speed   |  |  |  |

|------------|---------|--|--|--|

| 140 MB     | 18 fps  |  |  |  |

| 84 MB      | 45 fps  |  |  |  |

| 68 MB      | 139 fps |  |  |  |

© 2020 MathWorks

Generate HDL

# **Deploy from MATLAB to a Variety of Hardware Platforms**

#### **Resource Slide**

Deep Learning Solutions in MATLAB

https://www.mathworks.com/solutions/deep-learning.html

Deep Learning HDL Toolbox

https://www.mathworks.com/products/deep-learning-hdl.html

Onramp: Deep Learning in MATLAB

https://www.mathworks.com/learn/tutorials/deep-learning-onramp.html

MathWorks FPGA Solutions Page

https://www.mathworks.com/solutions/fpga-asic-soc-development.html

© 2020 MathWorks