## 2023 embedded VISION SUMMIT

# Fast-Track Design Cycles Using Lattice's FPGAs

Hussein Osman Marketing Director Lattice Semiconductor

## **Embedded Vision Trends**

Support multiple sensors and displays

Move to higher resolutions and faster frame rates

Connect MIPI and legacy components

Ena at I

Enable AI processing at low power These trends require hardware with:

- Low Power

- Small Form Factor

- High Performance

- High Reliability

- Ease of Use

## **Edge Processing Challenges**

Edge devices typically run on battery and are thermally challenged requiring low power profile

Rapidly changing deep learning AI algorithms

Heterogenous compute is required with HW accelerators assisting CPUs

GPUs used as accelerators best when executing the same instruction in parallel, also power hungry

#### Getting to market quickly

Compute requirement doubling every 3 month, 7x faster than Moore's law

SoC based heterogeneous compute is rigid, the HW accelerators are not programable

Spinning new versions of ASICs and ASSPs is costly limiting the update cycle of the HW blocks

#### FPGA adaptable architecture is required to accelerate compute efficiently

## Why FPGA for Edge AI

Lattice Semiconductor (NASDAQ: LSCC)

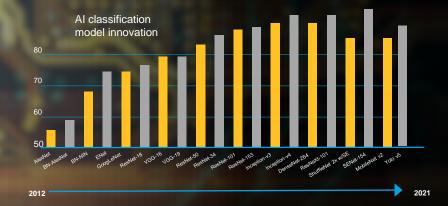

## The Speed of AI Innovation Benefits Programmable Logic to Keep Delivering the Best Experience.

embedded VISION SUMMIT

Algorithm optimization

#### AI models are rapidly evolving

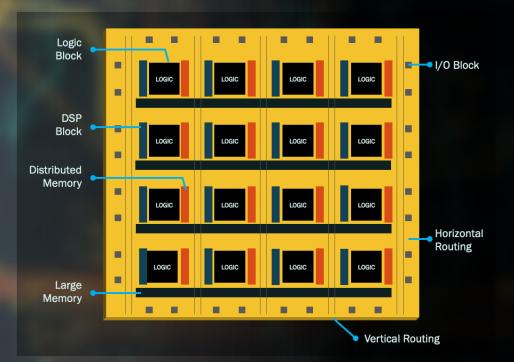

## **FPGA Architecture – Programable Distributed Resources**

embedded VISION SUMMIT

- Building blocks are distributed throughout the fabric

- Extensive interconnect routing connecting blocks

- Flexible I/Os to move data in and out

- Similar approach to modern AI ASICs

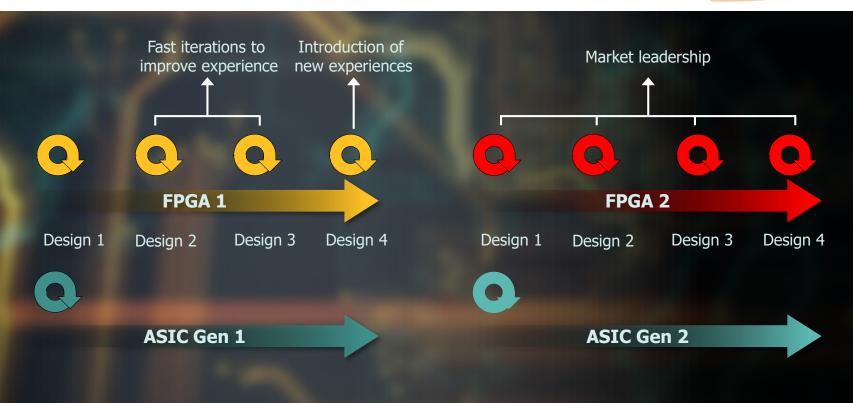

## AI Models Evolve Rapidly, Requiring Agile Development Cycles that ASICs Cannot Match

embedded

SUMMI

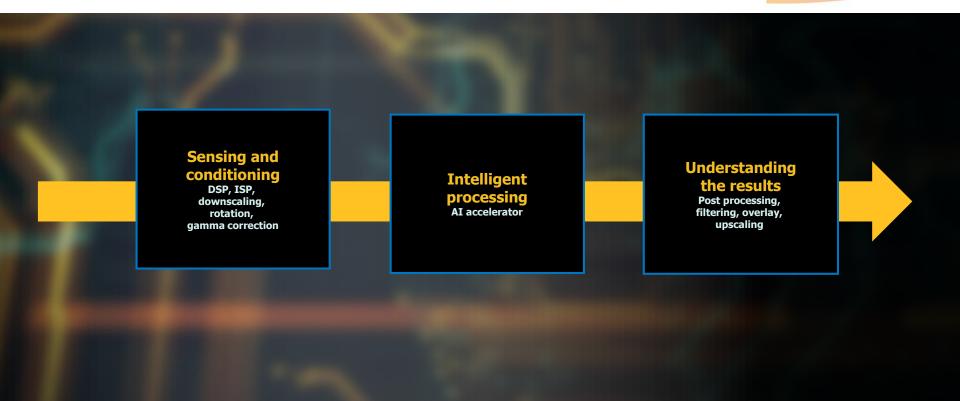

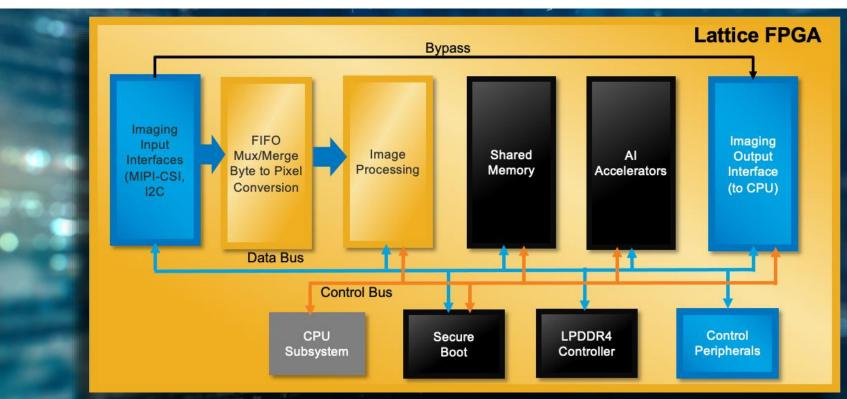

## **Vision Pipeline: End-to-end Hardware Implementation**

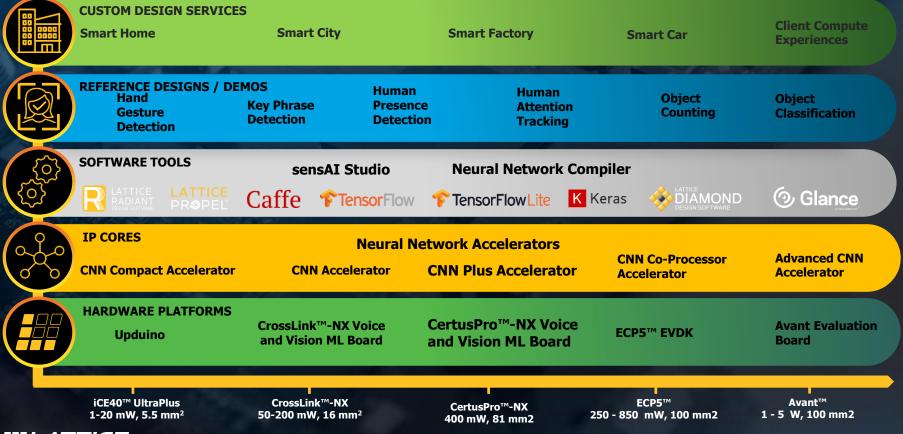

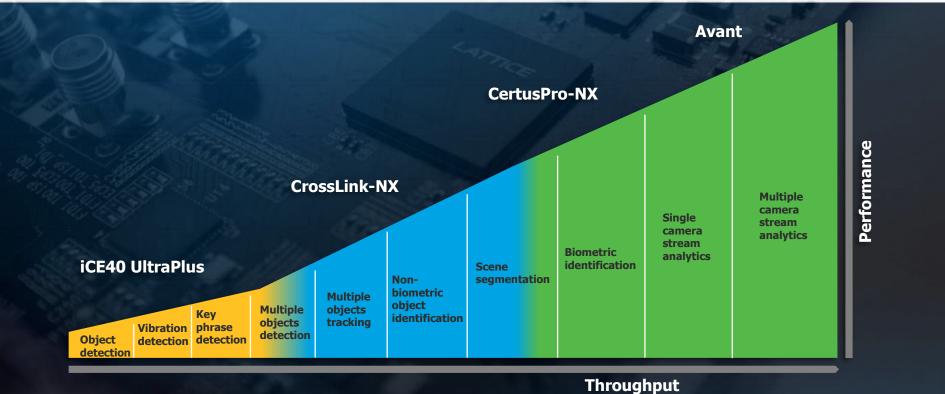

## **Applications Supported Across FPGAs**

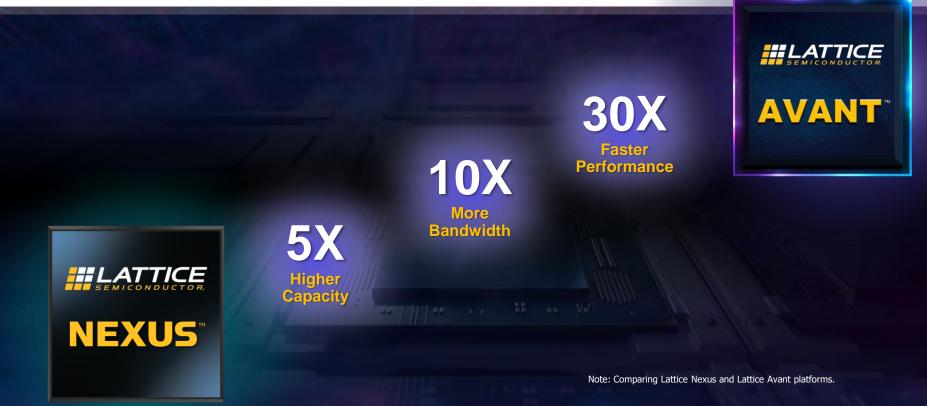

## **Advancement in Mid Range FPGAs**

SEMICONDUCTOR

Lattice Semiconductor (NASDAQ: LSCC)

# LATTICE AVANT

#### OPTIMIZED COMPUTE

- Enhanced DSP tuned for AI inferencing

- Flexible and distributed embedded memory

**On-Chip Compute Elements**

#### POWER EFFICIENCY

- Programmable fabric architected for low power

- Power optimized embedded memory and DSP

- Power efficient SERDES and I/O designs

- Built-in protocol logic for lower system power

#### ADVANCED CONNECTIVITY

- Configurable 25G SERDES Dedicated PCIe<sup>®</sup> Gen 4 x8 controllers

- Programmable high performance I/O

- High speed memory interfaces up to DDR5

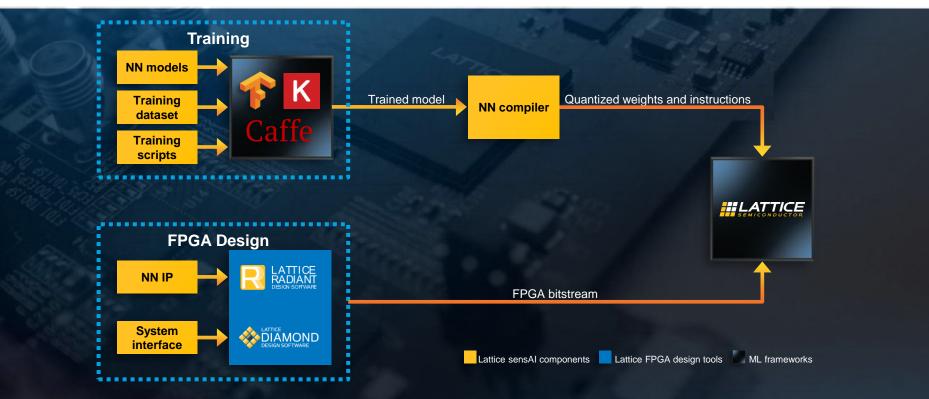

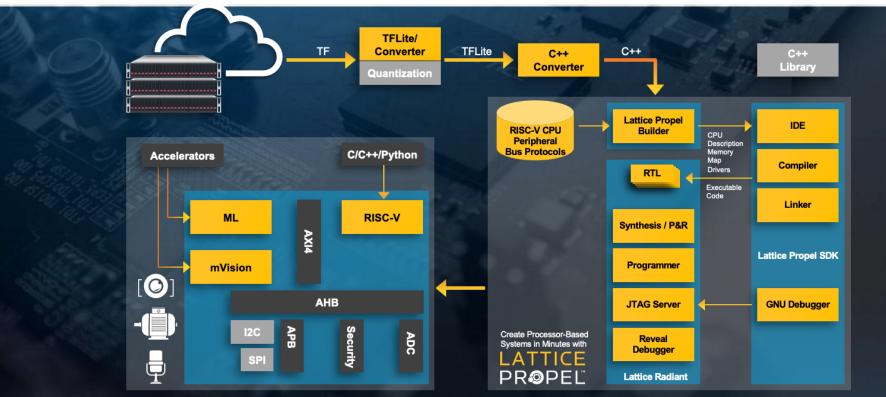

## **Hardware Optimized Design Methodology**

## **Software Optimized Design Methodology**

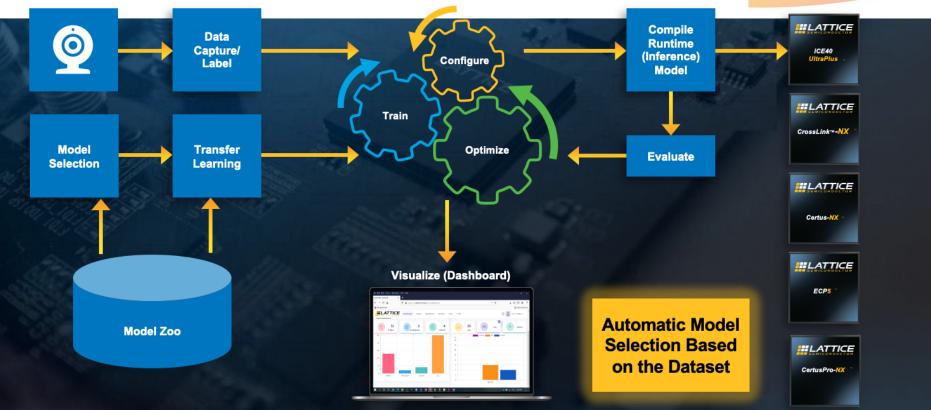

## Lattice sensAI Studio

## **Example FPGA Implementation for Computer Vision**

embedded

VISION SUMMIT

## **Object Classification – Real Time Video Analysis**

| Features              |                           | System Block Diagram |                                                            |                                                               |

|-----------------------|---------------------------|----------------------|------------------------------------------------------------|---------------------------------------------------------------|

| Video input           | 1080P                     |                      | HDMI Parallel                                              | Avant Evaluation Board                                        |

| Inferencing speed     | 77 FPS (17x CertusPro-NX) |                      | HDMI Port<br>Processor (TX)<br>HDMI Port<br>Processor (RX) | Video Output<br>Video Input<br>Video Input<br>Crop Down Scale |

| Power                 | 1.6 W (4x CertusPro-NX)   | Display              |                                                            |                                                               |

| Processing resolution | 480 x 288                 | Video<br>Player      |                                                            |                                                               |

| NN model              | Mobilenet v2              |                      |                                                            |                                                               |

| FPGA         | Engine       | # of DSP<br>Engines | # of INT8<br>Multipliers | FPGA Resources<br>Usage | FPS |

|--------------|--------------|---------------------|--------------------------|-------------------------|-----|

| Avant 500    | Advanced CNN | 272                 | 1088                     | 15%                     | 77  |

| CertusPro-NX | Advanced CNN | 72                  | 144                      | 32%                     | 10  |

| CrossLink-NX | CNNPlus      | 18                  | 36                       | 46%                     | 5   |

## **Creating Ready for Production Solutions**

# SEMICONDUCTOR.

# O MIRAMETRIX<sup>™</sup>

#### .....

..........

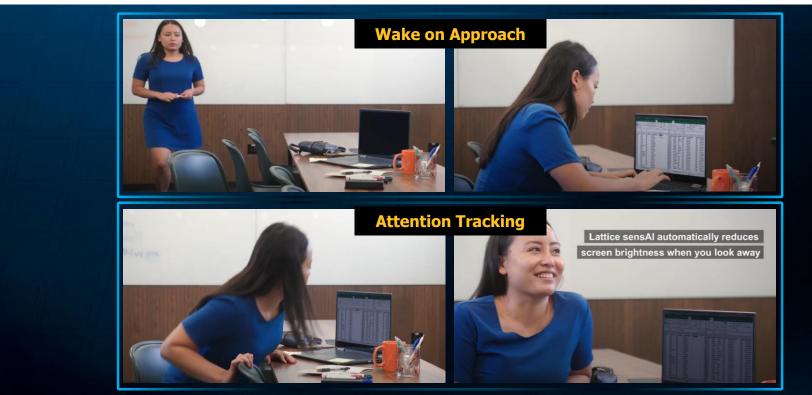

**Presence Detection**

Depth Sensing

3D Head & Gesture Tracking

Face ID & Landmarks Tracking

Eye Feature Detection & Tracking

Human Skeleton Detection

**Object Detection**

Advanced AI Technology for the Edge

## **Essential Features**

## **Privacy & Security**

CE SEMICONDUCTOR

Lattice Semiconductor (NASDAQ: LSCC)

## **Summary and Takeaways**

- Edge AI challenges require adaptable architecture for continued innovation

- FPGAs' programmability allows tinkering with the end-to-end designs before and after production

- A hardware-programable AI accelerator allows systems to evolve with new AI models

- Vision applications need flexible acceleration for the entire pipeline

- New class of mid range FPGAs come with DSP, memory and I/O advancement

- Tools, IPs and examples designs accelerate time to market

- Production-ready solutions can be customized and embedded into different applications

## **Demos and Additional Resources**

Booth #317, Santa Clara Convention Center 5001 Great America Parkway, Santa Clara, CA 95054 May 23, 12:30 pm – 7:30 pm | May 24, 10:30 am – 6:00 pm

### **EXPERIENCE THE LATEST ADVANCEMENTS IN FPGAs**

At Lattice, we are committed to providing our customers with innovative FPGA hardware and software solutions that help them bring exciting new features and capabilities to the market. We invite you to visit us at Embedded Vision Sumit 2023 to experience our latest technology and meet with our team face-to-face.

Discover the Lattice technology powering Industrial, Automotive, Computing, and Consumer IoT applications at the Edge. See how our low power, small form factor, secure FPGAs based on our award-winning Lattice Avant<sup>™</sup> and Lattice Nexus<sup>™</sup> FPGA platforms enable advanced embedded vision and machine learning capabilities. Learn how our application-optimized solution stacks can help accelerate time to market across multiple segments.

The Low Power Programmable Leader