# Using MIPI CSI to Interface with Multiple Cameras

Karthick Kumaran Ayyalluseshagiri Viswanathan Staff Software Engineer Meta Platforms Inc

#### **Topics**

- Camera Interfaces

- Quick Recap MIPI

- SoC Camera Architecture

- MIPI CSI D-PHY

- MIPI CSI C-PHY

- Virtual Channel (VC)/ Data Type (DT) Aggregation

- Multi-Drop

- Summary

#### **Problem Statement**

- Growing number of advanced use cases in robotics, VR/AR, drones, and automotive, demand multiple cameras

- Limited number of camera interfaces limits the number of cameras connected to the SOC

- Will cover various techniques to overcome the limitations

#### **Camera Interfaces**

- Parallel interface

- USB

- MIPI

I will be covering only the MIPI interface in this talk

#### **MIPI CSI-2**

- CSI for camera

- A-PHY (for automotive)

- C-PHY (trio)

- D-PHY (Differential phase)

- DSI for display

## **Quick Recap of MIPI CSI-2 Frame Format**

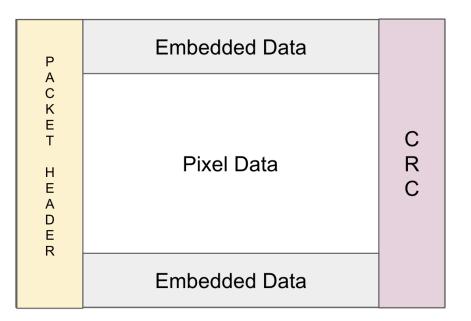

- Two types of MIPI packets

- Short packet

- Long packet

- Short packet

- Packet header (PH)

- Long packet

- Packet header

- 8-bit data identifier

- 2-bit VC + 6-bit DT

- 16-bit word count

- 8-bit ECC

- Payload Pixel data

- Packet footer

#### Architecture

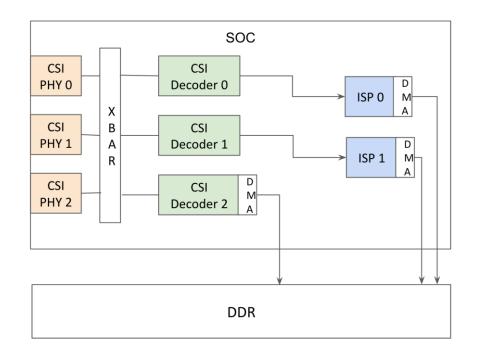

- Typically, SOCs have several number of hardware blocks such as

- MIPI CSI PHY interfaces

- MIPI CSI decoders

- ISPs

- DMAs

- Number of hardware blocks vary between SOCs

#### Inline ISP

#### Architecture

- CSI PHY used to interface

- Camera sensors

- Depth sensors

- DTOF / ITOF etc.,

- CSI decoder to decode the MIPI protocol

- DMA to transfer the pixels to DDR

- ISP to perform image processing

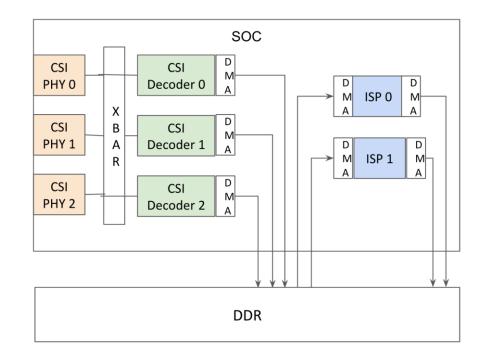

#### Offline ISP

#### CSI PHY, CSI Decoder & ISP

- There are a fixed number of CSI PHY interfaces, CSI decoders and ISPs available on embedded SoCs

- Number of CSI Interfaces and number of CSI decoders need not be always the same

- Similarly, number of CSI decoders and number of ISPs need not be always the same

- Color cameras need ISP to do demosaic and image quality enhancements

- Monochrome cameras for computer vision / deep learning algorithms

- May not need any ISP processing

- Cross bar between CSI PHY interface and CSI decoder helps to map them arbitrarily

- ISP to perform image processing such as

- Demosaic, color space conversion (CSC), black level subtraction (BLS), gamma, scale, crop and other IQ enhancements

- Inline ISP

- Pixels are passed to the ISP directly from the CSI decoder

- Less latency

- Less power consumption as it avoids round trip to the DDR

- Offline ISP

- Acts like M2M (Memory-to-Memory) device

- Higher latency than inline ISP

- Supports multiple instances

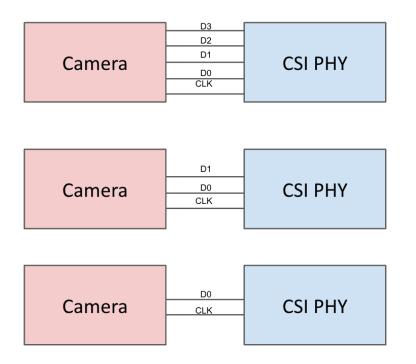

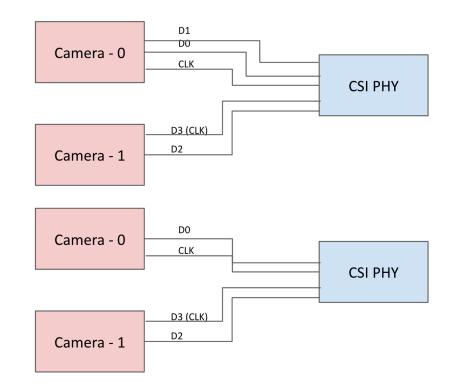

#### **MIPI CSI D-PHY**

- Up to 4 data lanes can be connected to a single CSI PHY in D-PHY mode + 1 clock lane

- High resolution cameras use all the 4 data lanes

- Mid to low resolution cameras use either 2 lanes or 1 lane

## Meta

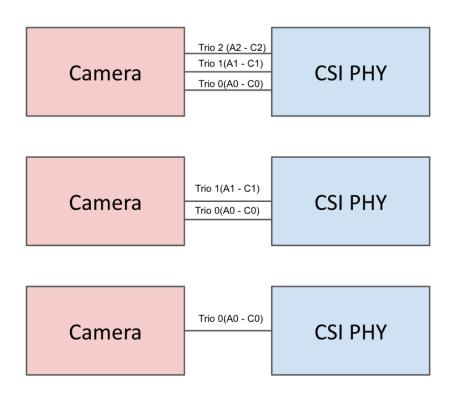

#### **MIPI CSI C-PHY**

- Up to 3-trios can be connected to a single CSI PHY in C-PHY mode

- High resolution, high fps cameras use all the trios

- Lower resolution (less bandwidth) cameras uses either 2 trios or single trio

- Faster than D-PHY

#### **CSI** Split

- Two low resolution cameras can be connected to a single CSI PHY

- 2-lanes + 1-lane configuration

- 1-lane + 1-lane configuration

- Dedicated CSI decoder required for each camera to operate concurrently

- With one CSI decoder

- One of the camera can be enabled

- Allows switching cameras

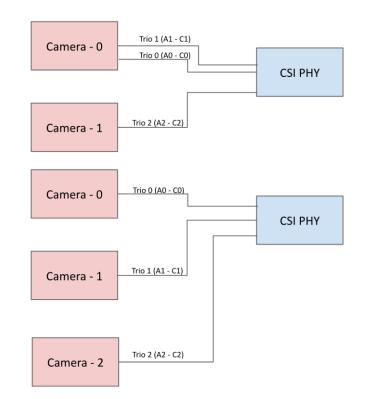

## **CSI Split (continued)**

- Up to 3 low resolution cameras can be connected to a single CSI PHY

- 2-trio + 1-trio

- 1-trio + 1-trio + 1-trio

- 1-trio + 1-trio

- Dedicated CSI decoder required for each camera to operate concurrently

- With one CSI decoder

- One of the camera can be enabled

- Allows switching cameras

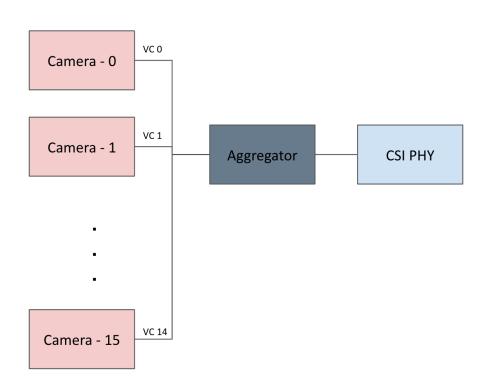

#### Virtual Channel / Data Type Aggregation

- Multiple cameras, up to 16, can use the single CSI PHY interface

- Aggregator is needed

- Uses TDM (Time Division Multiplexing)

- Aggregator has to manage the TDM

- Uses MIPI virtual channels (VC)

- Single CSI decoder can decode MIPI packets from all the cameras as they are time multiplexed

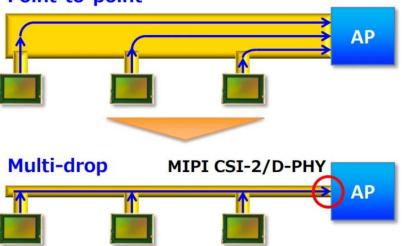

#### **Multi-drop**

- Multiple sensors (usually 2-to-4) can be connected to a single MIPI D-PHY port

- Limits the frame rate of each sensor based on the data rate and the number of lanes

- Same virtual channel for all the sensors

- Unique virtual channel for each sensor

- Works only with global shutter cameras

#### Point-to-point

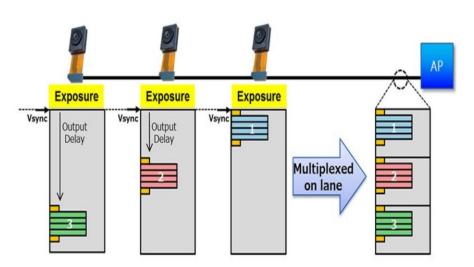

#### **Multi-drop (continued)**

- Some cameras supports a feature named "Multi-drop" which enables us to connect more than 1 camera without an aggregator

- Uses different exposure time / readout time

- Can use different VCs for each cameras

- Can use same VCs for all the cameras (super frame)

- MIPI CSI protocol provides lot of flexibility to connect multiple cameras to the CSI PHY interfaces

- MIPI CSI protocol provides a mechanism to multiplex multiple camera sensor data in time division multiplex mechanism

- Helps reduce the footprint of the SOC

#### Resources

• MIPI CSI-2 Specification - <u>https://www.mipi.org/specifications/csi-2</u>

#### Thank You