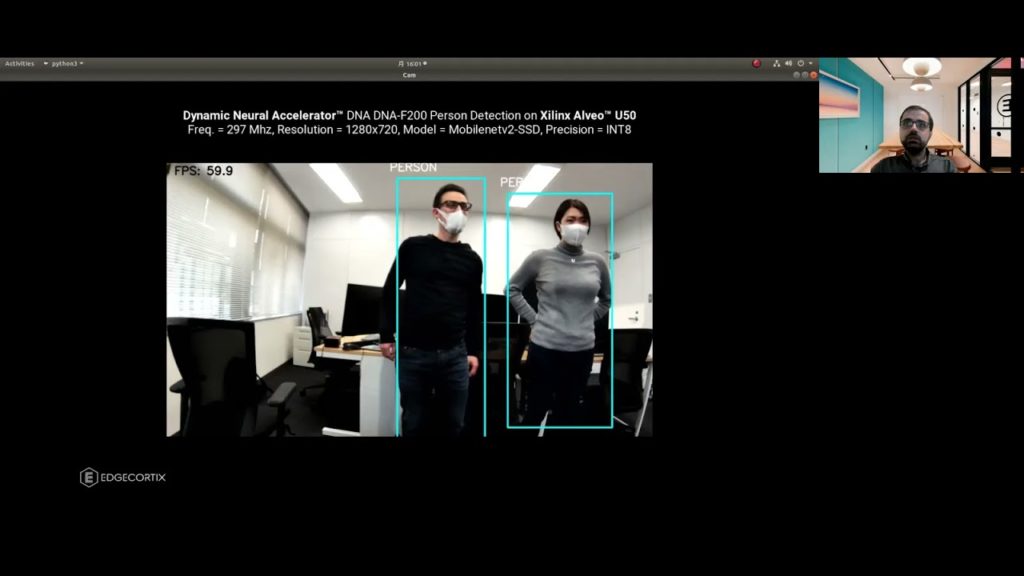

Hamid Zohouri, Director of Product at EdgeCortix, demonstrates the company’s latest edge AI and vision technologies and products at the 2021 Embedded Vision Summit. Specifically, Zohouri demonstrates the company’s Dynamic Neural Accelerator (DNA) F-series architecture and MERA compiler for low-latency deep neural network (DNN) inference.

EdgeCortix’s DNA architecture is a runtime-reconfigurable, highly scalable and power-efficient AI processor design that works on FPGAs as well as custom ASICs and systems on chips (SoCs). This demo showcases the different configurations of EdgeCortix’s DNA F-series AI engines for FPGAs currently available for customers. It also introduces the MERA compiler that works together with the DNA F-series to enable the deployment of DNNs for computer vision applications, achieving real-time AI inference with high resolution still image and video data. Also shown are video demos of typical use-case applications of AI inference in Xilinx FPGA-enabled edge servers and embedded SoCs.